PCB线路板阻抗线设计注意事项

在PCB线路板设计中,阻抗线的设计是确保高速信号完整性的核心环节。随着电子设备性能的不断提升,信号频率逐渐向高频甚至射频方向发展,这使得阻抗控制成为设计中的关键步骤之一。以下从多个方面详细探讨了阻抗线设计中的注意事项,帮助设计师更好地应对实际项目中的挑战。

- 叠层设计

介质参数匹配:与板厂确认材料的介电常数(Dk)、介质厚度、铜厚,确保叠层结构满足阻抗要求。

对称设计:建议采用对称叠层(如8层、12层板)以降低翘曲风险,并确保阻抗一致性。

- 线宽与间距

阻抗公式计算:使用阻抗计算工具(如Polar SI9000),结合叠层参数优化线宽和间距。

避免突变:线宽变化会导致阻抗不连续,需保持均匀走线,必要时渐变过渡。

间距规则:相邻信号线间距≥3倍线宽(例如50Ω单端线宽0.2mm,间距≥0.6mm),防止串扰。

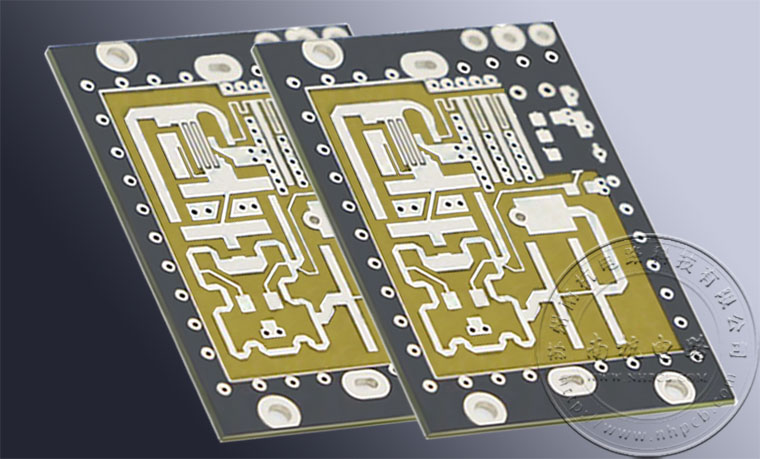

- 介质材料选择

高频材料:对于GHz级高速信号(如USB3.2、PCIe 4.0),优先选用低损耗材料(如Rogers 4350B,Dk=3.48±0.05)。

常规材料控制:FR-4需关注Dk波动(典型值4.5±0.4),设计时需留±10%余量。

- 参考平面

完整参考地:阻抗线正下方需保持完整参考平面,避免跨分割(如避开电源平面分隔处)。

跨层参考:多层板中,若必须换层,需在换层位置200mil内增加回流地过孔(每毫米至少1个)。

- 差分线对称性

等长等距:差分对长度偏差≤5mil(如USB3.0要求≤15mil),间距误差控制在±10%。

蛇形绕线:绕线幅度≤3倍线宽,间距≥5倍线宽,优先外层绕线(避免内层介质损耗)。

- 过孔优化

残桩控制:使用背钻技术(如20层HDI板)将残桩长度缩短至8mil以内。

过孔电容补偿:在BGA下方采用Via-in-Pad设计时,通过减小焊盘直径(如0.25mm→0.2mm)降低寄生电容。

- 制程能力匹配

线宽公差:与板厂确认精度(如±0.5mil),预留10%设计余量。

表面处理:沉金(ENIG)对阻抗影响约2%,需提前仿真补偿。

- 测试验证

TDR测试:实际板卡阻抗偏差控制在±7%内(如PCIe 5.0要求±8%)。

测试结构:板边预留阻抗测试条,覆盖所有阻抗类型(单端85Ω/差分90Ω等)。

- 走线拓扑优化

避免直角:45°走线相比直角可降低反射幅度20dB。

弧形转角:10GHz信号优先采用曲率半径≥3倍线宽的圆弧走线。

案例说明:某10层服务器主板设计中,为DDR4-3200设计50Ω单端阻抗线:

采用FR4材料(Dk=4.3),计算线宽为4.8mil(内层),介质厚度3.2mil。

参考平面选用完整地平面层,线间距设定为15mil。

换层时在过孔周围0.5mm内增加4个地过孔。

板厂最终测试阻抗48.5Ω(误差-3%),满足设计要求。

关键原则:通过参数精确控制+仿真验证+制程协同,实现阻抗目标。设计中建议保留10%设计余量,并建立板厂阻抗模型库。